您现在的位置是:首页 >要闻 > 2021-01-08 08:18:33 来源:

在超导量子位架构中实现XY纠缠门的新策略

在过去的大约十年中,全球的研究团队一直在尝试开发用于量子信息处理的设备和硬件组件。这些新兴设备中大多数的性能很大程度上取决于优化的电路实现方式,可以使电路深度最小化。

实现此目的的一种可能方法是使用更昂贵,更复杂的本机门。事实证明,XY两量子位闸对于减少通用电路的深度特别有希望,同时还可以改善量子处理器在特定问题上的性能。

Rigetti Computing的研究人员最近展示了使用XY纠缠门改善基于tansmon的超导量子位架构的性能的潜力。在《自然电子》上发表的一篇论文中概述了他们的方法,该方法仅需要使用单个校准脉冲。

进行这项研究的研究人员之一尼古拉斯·迪迪埃(Nicolas Didier)博士说:“为了提高量子处理器的性能,提供能表达的本机门集合以减少从算法到硬件的编译开销是有利的。”告诉Tech Xplore。“特别是对于变分量子算法,它有助于具有连续的纠缠门系列。在这项工作中,我们开发了跨子量子比特上XY系列的有效实现。”

迪迪埃和他的同事们设计了一种新的策略,用于在基于跨门的超导量子位架构中实现纠缠门。这种方法允许他们通过施加通量脉冲来控制体系结构中qubit-qubit交互的相位。

“要生成完整的XY系列,我们只需将iSWAP门分成两个√iSWAP门,并在两者之间改变相位,” Didier说。“整个系列是通过仅对√iSWAP的脉冲进行校准而获得的,它提供了一种有效的方法来定期重新调谐我们部署的量子处理器。(iSWAP = XY(π)和√iSWAP= XY(π/ 2),iSWAP的平方根)。”

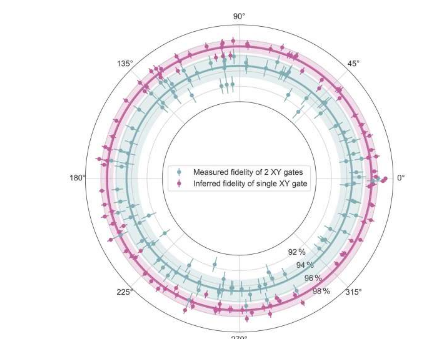

新策略使XY纠缠门能够在其所应用的超导系统中实现,并具有很高的保真度。Didier及其同事还证明了他们的方法可用于实现量子近似优化算法,与仅基于CZ门的策略相比,可将电路深度减少约30%。

迪迪尔说:“我们生成的XY门系列的保真度在96%至99%之间。” “这些门在动态最佳点上运行,以减轻由于缓慢的通量噪声引起的相移。我们还说明了QAOA算法上的本机门表达集的优势,表明将iSWAP和CZ结合使用可使门深度减少30%。 ”

这组研究人员提出的策略最终可以为性能更好,效率更高的量子信息处理器的开发提供信息。在他们的论文中,研究人员表明,他们的门分解策略可以扩展到其他类型的本机门,这可以进一步减小电路深度。

迪迪埃说:“我们的方法可以通过仅校准两个脉冲,扩展到两个相位的CPHASE系列的CPHASE系列和三个相位的CCPHASE系列的CCPHASE系列,与以前的实现相比,其深度减少了2-6倍。” “ Rigetti量子处理器的用户可以尝试使用我们的脉冲级控制界面Quil-T来减小编译后的门深度。”